# A RISC-V SystemC-TLM simulator

**CARRV 2020**

Màrius Montón

# Outline

- Introduction

- Simulator

- Tests

- Conclusions

Motivation

# **Motivation**

Develop a simple simulator based on a RISC-V CPU

- As a embedded processor

- Small CPU

- Simple memory scheme

- Using a simple toolchain

- Out-of-the-box binary from gcc

- Easy tools

- No semi-hosting facilities

- And easy expandable

- Attach new peripherals

- Add new RISC-V extensions

- Modify CPU architecture

SystemC as language

- C++ based, well known language

- Add-ons HW to C++

- Simulation based

- Possibility to synthesis with external tools

TLM-2 as modeling

- Transaction based

- Common interface

**TLM Transactions & sockets**

- Communication channel

- Abstraction of a bus

- Details not important

- Information about time and address/data

- Increase simulation speed

- Sockets encapsulates all this

- Initiator/Target <--> Master/Slave

- Interchangeable

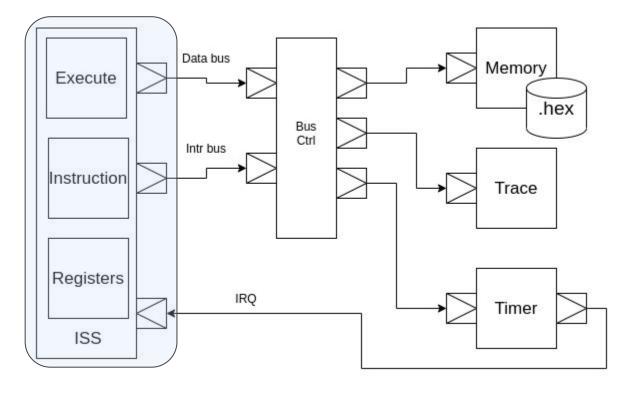

#### Instruction set simulator

- Execute and decode

- Extensions

- Register file

- o x0-x31

- **PC**

- CSR

- Harvard

- Data / Instr. Bus

- IRQ port

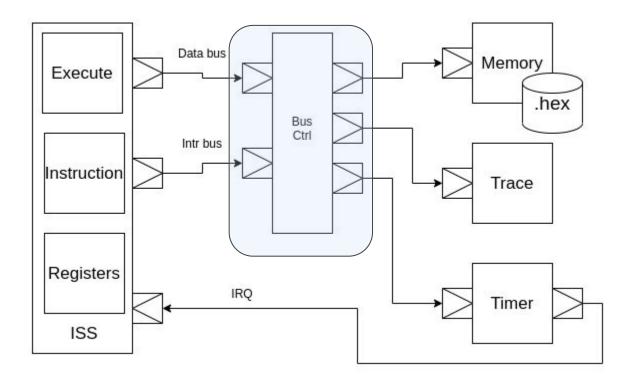

### Bus controller

- Data / Instr. Input sockets

- Out sockets

- $\circ$  To memory

- Peripherals

- Trace

- Timer

- Memory map

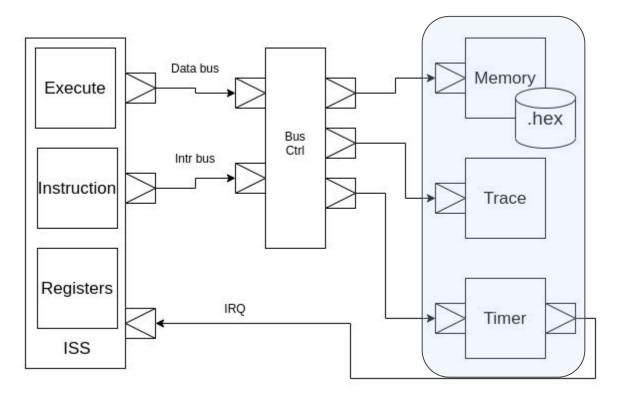

### Peripherals

- Memory

- Exe file pre-loaded

- Trace for debug/console

- Timer, trigger IRQ

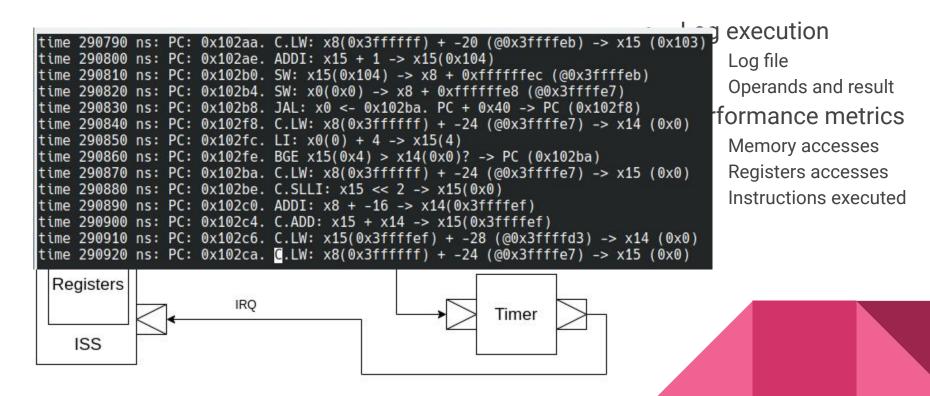

### Simulation helper

- Log execution

- Log file

- $\circ \quad \text{Operands and result} \quad$

- Performance metrics

- Memory accesses

- Registers accesses

- Instructions executed

#### Simulation helper

| ****                        | ****        |              |                   | _ |

|-----------------------------|-------------|--------------|-------------------|---|

| Registers dump              |             |              |                   |   |

| x0 (zero):                  | 0 x1 (ra):  | 0 x2 (sp):   | 67108863 x3 (gp): | 0 |

| x4 (tp):                    | 0 x5 (t0):  | 0 x6 (t1):   | 0 x7 (t2):        | 0 |

| x8 (s0/fp):                 | 0 x9 (s1):  | 0 x10 (a0):  | 0 x11 (a1):       | 0 |

| x12 (a2):                   | 0 x13 (a3): | 0 x14 (a4):  | 10 x15 (a5):      | 9 |

| x16 (a6):                   | 0 x17 (a7): | 0 x18 (s2):  | 0 x19 (s3):       | 0 |

| x20 (s4):                   | 0 x21 (s5): | 0 x22 (s6):  | 0 x23 (s7):       | 0 |

| x24 (s8):                   | 0 x25 (s9): | 0 x26 (s10): | 0 x27 (s11):      | 0 |

| x28 (t3):                   | 0 x29 (t4): | 0 x30 (t5):  | 0 x31 (t6):       | 0 |

| PC: 0x0                     |             |              |                   |   |

| *****                       | *****       |              |                   |   |

| Simulation time             | 1020 ns     |              |                   |   |

| <pre># data memory re</pre> | ads: 0      |              |                   |   |

| # data memory wr            |             |              |                   |   |

| <pre># code memory re</pre> |             |              |                   |   |

| # code memory wr            |             |              |                   |   |

| <pre># registers read</pre> |             |              |                   |   |

| <pre># registers writ</pre> |             |              |                   |   |

| <pre># instructions e</pre> |             |              |                   |   |

|                             |             |              |                   |   |

|                             | Z IRQ       | 2            | → > Timer >       |   |

|                             | < •         |              |                   |   |

| 100                         |             |              |                   |   |

| ISS                         |             |              |                   |   |

|                             |             |              |                   |   |

|                             |             | L            |                   |   |

#### Simulation helper

Lag avaaution

|             | Log ex       | ecution       |        |

|-------------|--------------|---------------|--------|

| 0           | • Lo         | g file        |        |

| 0           | • <b>Op</b>  | erands and r  | esult  |

| 9<br>0<br>0 | Perfor       | mance me      | trics  |

| 0           | • <b>M</b> e | emory access  | ses    |

|             | • Re         | gisters acces | sses   |

|             | • Ins        | tructions exe | ecuted |

|             |              |               |        |

|             |              |               |        |

|             |              |               |        |

|             |              |               |        |

|             |              |               |        |

|             |              |               |        |

|             |              |               |        |

Pure bare-metal simulator

- ECALL, EBREAK  $\rightarrow$  implemented to help debugger, not calling OS

- ECALL Stops simulation

- EBREAK Raise Breakpoint exception

- Need to implement \_write() \_read() functions in sim code

- Support full C std libraries for sim code

- FreeRTOS porting

Docker version

- Not need to compile anything, just hit & run

- Performance penalty

Pure bare-metal simulator

- ECALL, EBREAK  $\rightarrow$  implemented to help debugger, not calling OS

- ECALL Stops simulation

- EBREAK Raise Breakpoint exception

- Need to implement \_write() \_read() functions in sim code

- Support full C std lib #define TRACE (\*(unsigned char \*)0x4000000)

- FreeRTOS porting

Docker version

- Not need to compile

- Performance penalty

```

int _write(int file, const char *)0x40000000)

int _write(int file, const char *ptr, int len) {

int x;

for (x = 0; x < len; x++) {

TRACE = *ptr++;

}

return (len);</pre>

```

Pure bare-metal simulator

- ECALL, EBREAK  $\rightarrow$  implemented to help debugger, not calling OS

- ECALL Stops simulation

- EBREAK Raise Breakpoint exception

- Need to implement \_write() \_read() functions in sim code

- Support full C std libraries for sim code

- FreeRTOS porting

Docker version

- Not need to compile anything, just hit & run

- Performance penalty

Tool-chain

- Used gcc for RISC-V

- Only small CFLAGS required

```

CFLAGS = -Wall -I. -OO -static -march=rv32imac -mabi=ilp32

--specs=nosys.specs

```

- Default linker script

- Uses HEX file from elf output

> objcopy -Oihex file.elf file.hex

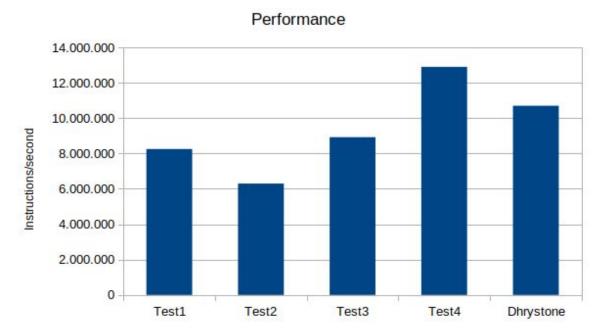

### Tests

Check ISS correctness - Compliance tests

- riscv/riscv-tests passed

- riscv-compliance test passed

Check whole simulator - C programs

- Simple C programs, using libraries

- FreeRTOS porting

- Dhrystone

- Consistent

- Penalty using trace

- Penalty using Log

Conclusions

# Conclusions

Simulator is working fine

- Complex programs running OK

- No cross-tools modifications

- Easy to use and understand

Need to add more components

- Add I/O peripherals

- Add FLASH memory for instr.

- Model a real MCU

### Conclusions

Increase performance, but similar to other SystemC simulators

**Open-Source**

https://github.com/mariusmm/RISC-V-TLM