# RISC5: Implementing the RISC-V ISA in gem5

Alec Roelke (ar4jc@virginia.edu)

Mircea R. Stan (mircea@virginia.edu)

#### Introduction

- Increasing complexities of designs increases simulation overhead

- Proprietary libraries and architectures impede research and collaboration

- Solution: gem5—fast, flexible, free

- Useful for RISC-V hardware development

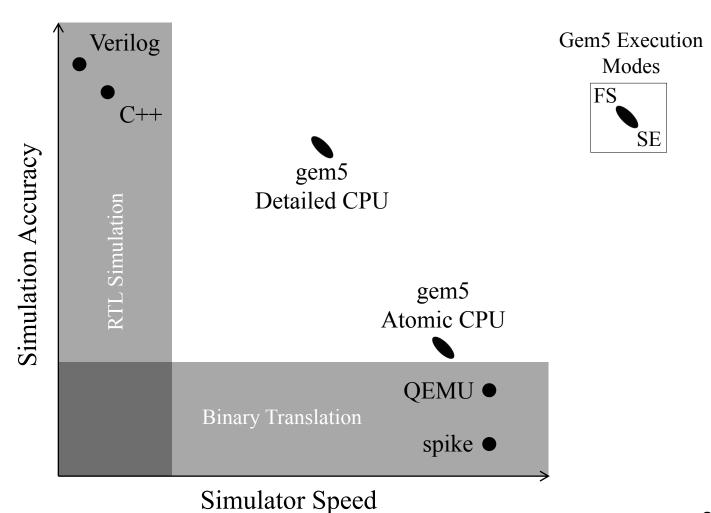

#### RISC-V Simulation Platforms

#### **Outline**

- Implementation of RISC-V in gem5

- Comparison with Other RISC-V Simulators

- Performance and Validation

- Example Simulation Flow

- Future Work

# Implementation of RISC-V in gem5

- Includes 64-bit base ISA + standard extensions (RV64G)

- Supports single-threaded execution in SE mode

- No support for privileged ISA yet

# Integer and Multiply Instructions

- Most instructions based on MIPS

- e.g. fence (RISC-V): sync (MIPS)

- Internal behaviors mostly copied from MIPS and Alpha

- Nearly all instructions implemented

- Only eret has no implementation

- fence does not support ordering flags

#### **Atomic Instructions**

- Release Consistency: acquire an address to see changes after earlier release

- LR/SC and atomic RMW instructions

- Mark instructions with ACQUIRE or RELEASE

- RMW needs two memory operations—not supported with memory timing!

- Split into two micro-ops and add intermediate register

## Floating-Point Instructions

- Development machine missing max magnitude round mode

- Verified against spike and a hardware design

- Invalid computation results (NaN, ∞, 0)

- Floating point exceptions

#### Simulation Features

| Feature                | gem5       | Chisel     | spike      | QEMU     |

|------------------------|------------|------------|------------|----------|

| Binary Translation     | <b>✓</b>   |            | <b>✓</b>   | <b>✓</b> |

| Checkpoints            | <b>✓</b>   |            |            | <b>✓</b> |

| Multicore Simulation   | <b>✓</b> † | <b>✓</b>   | <b>✓</b>   | <b>✓</b> |

| Performance Statistics | <b>✓</b>   | <b>✓</b> ‡ |            |          |

| RTL Simulation         |            | <b>✓</b>   |            |          |

| System Call Emulation  | <b>✓</b>   | ✓§         | <b>√</b> § |          |

<sup>§</sup>System call emulation is supported via the RISC-V proxy kernel

<sup>†</sup>Requires m5threads, which does not support RISC-V yet

<sup>‡</sup>Only with support from design and/or software

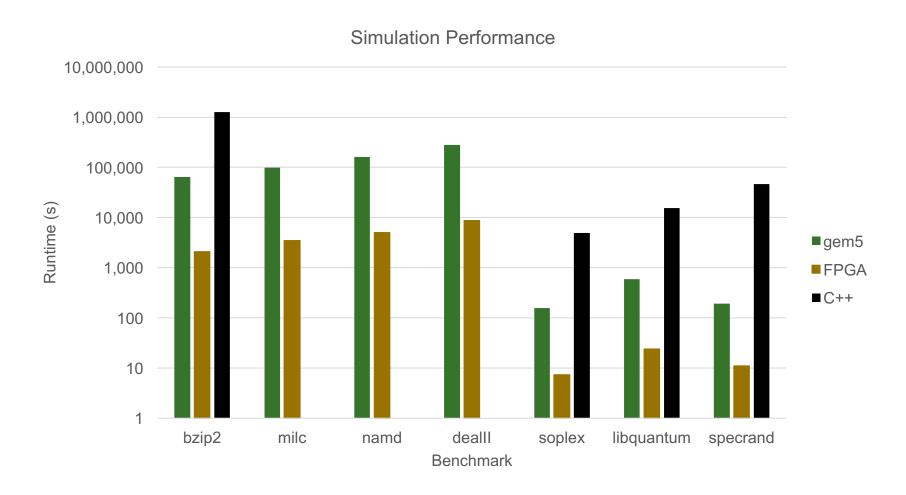

#### Performance and Validation

- Configure gem5 to resemble Rocket Chip

- Compare with FPGA and C++ simulator

- Run several SPEC CPU2006 benchmarks

### Performance Results

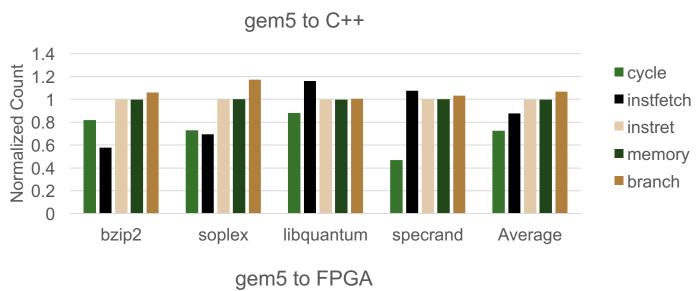

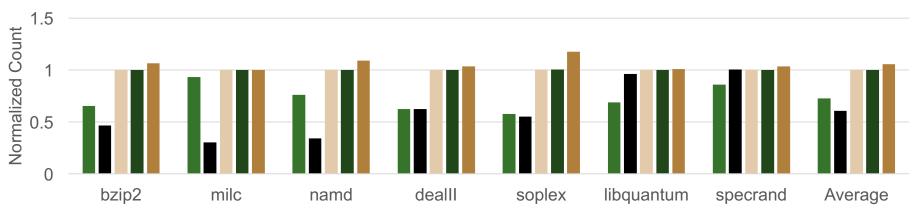

## Validation Results

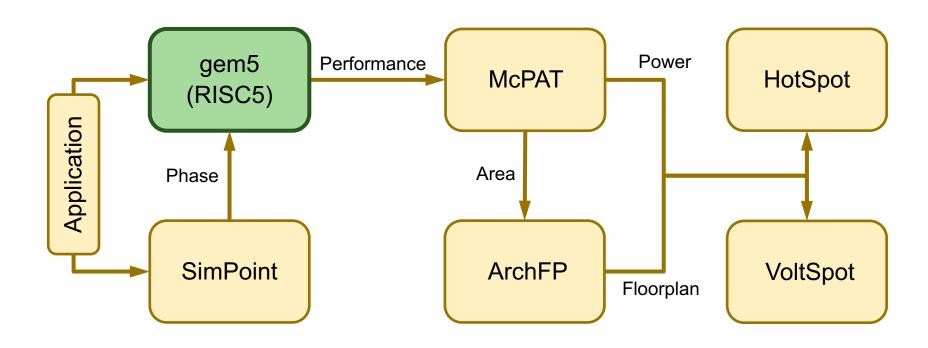

## **Example Flow**

- Simulate a section of the *libquantum* SPEC CPU2006 benchmark

- Exclude VoltSpot due to cycle-by-cycle input requirement

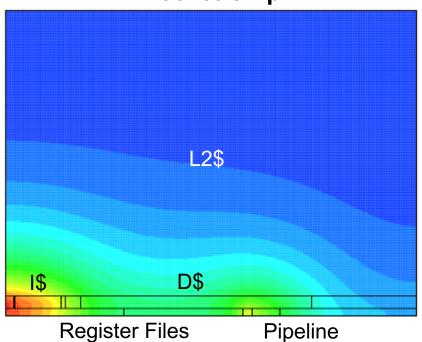

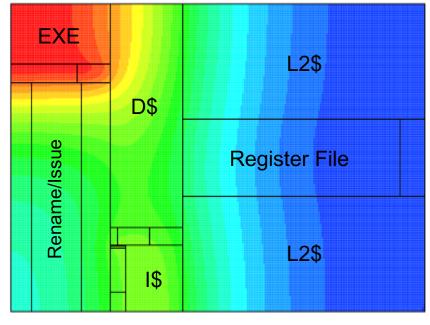

# **Example Results**

BOOM

Area: 4.175 mm<sup>2</sup> Power: 1.0215 W

Process Size: 45 nm Frequency: 1.5 GHz

V<sub>DD</sub>: 1.0 V

Area: 1.367 mm<sup>2</sup> Power: 5.1114 W

#### **Future Work**

- Full support for all of gem5's features

- Multithreaded workloads in SE mode

- Full-system mode

- Correct minor differences (e.g. floating-point rounding)

- Improve modeling accuracy

- Explore ISA effects on power/performance

# Acknowledgments

- Pradip Bose, Schuyler Eldridge, and the rest of the IBM VELVET Team

- Members of the HPLP research group

- The gem5 community

#### Conclusion

- Implemented RISC-V in gem5

- Compared with and validated against

Chisel C++ simulation and FPGA

- Executed an example simulation flow

- Significant work left until full support

- RISC5 is available as part of the main gem5 release at <u>www.gem5.org</u>

## Version Information

| Component      | Version                   |

|----------------|---------------------------|

| gem5           | ffc29f2d9a5a <sup>†</sup> |

| User-level ISA | 2.1                       |

| Privileged ISA | N/A                       |

| Rocket Chip    | 73e9508                   |

| Chisel         | b18e98b                   |